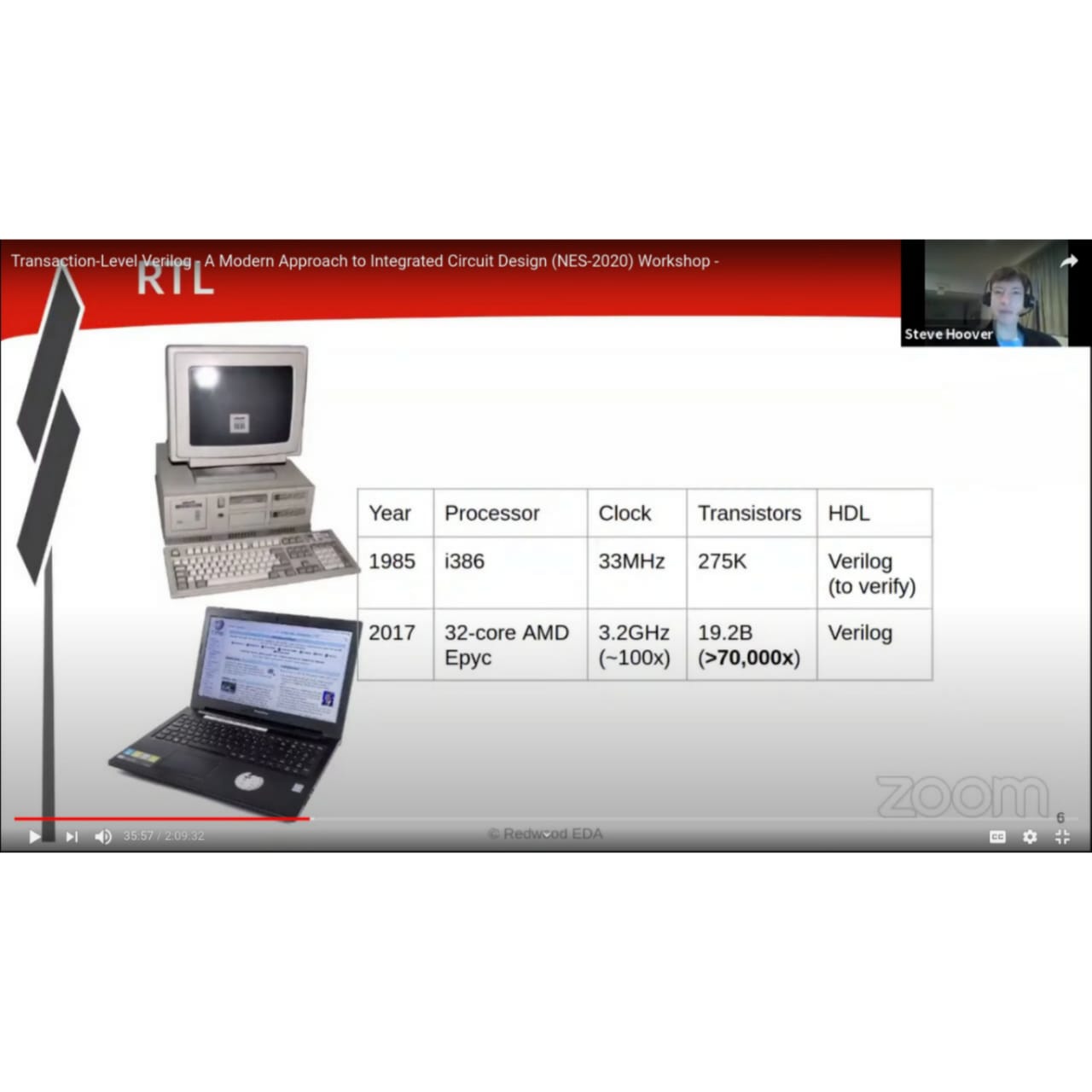

In verilog it took appx 1000 lines to design the whole code whether in TL-V 110 lines . A 10x better solution ... WOAAHHHHHHHHHHH.......

Now lets just talk a little bit about TL-V.

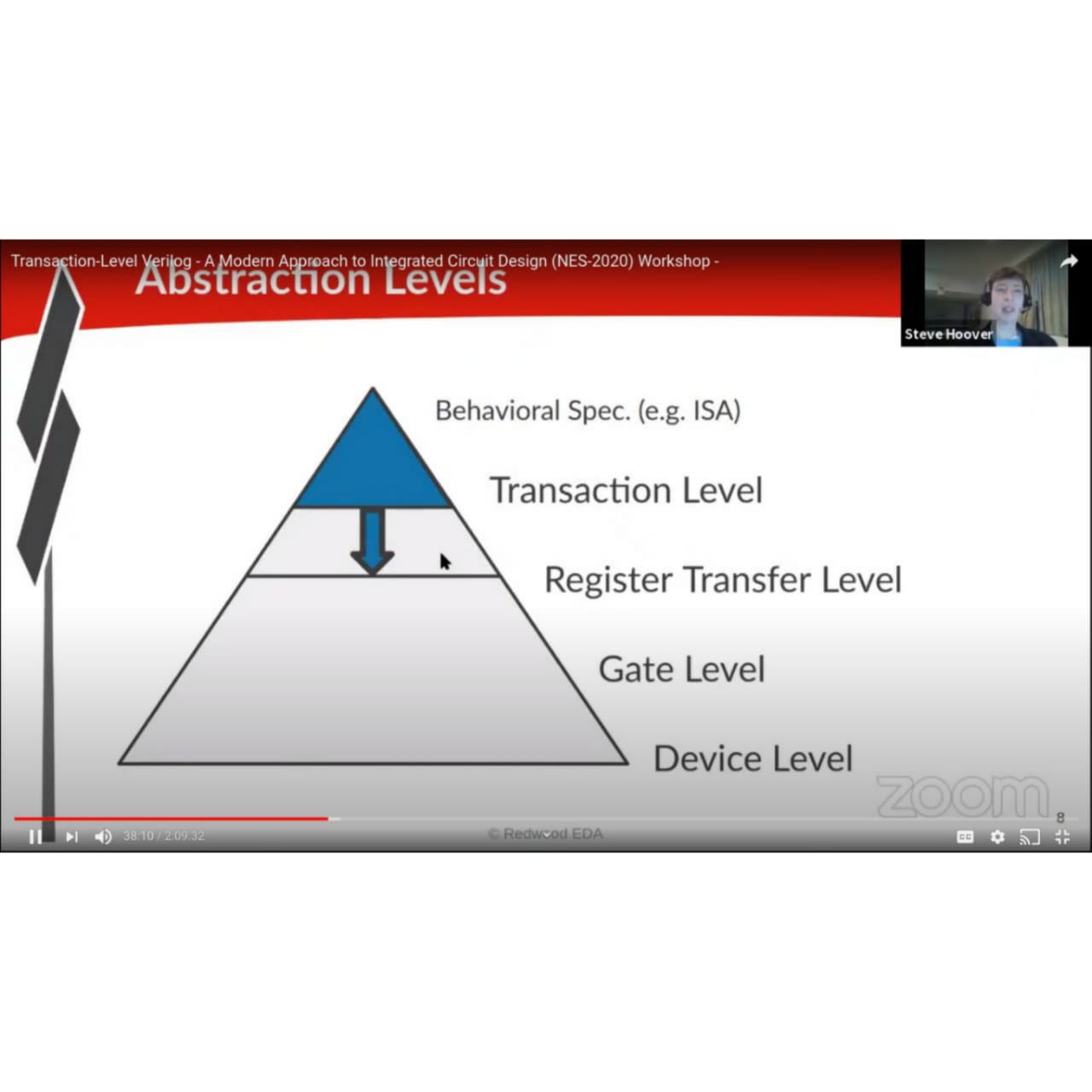

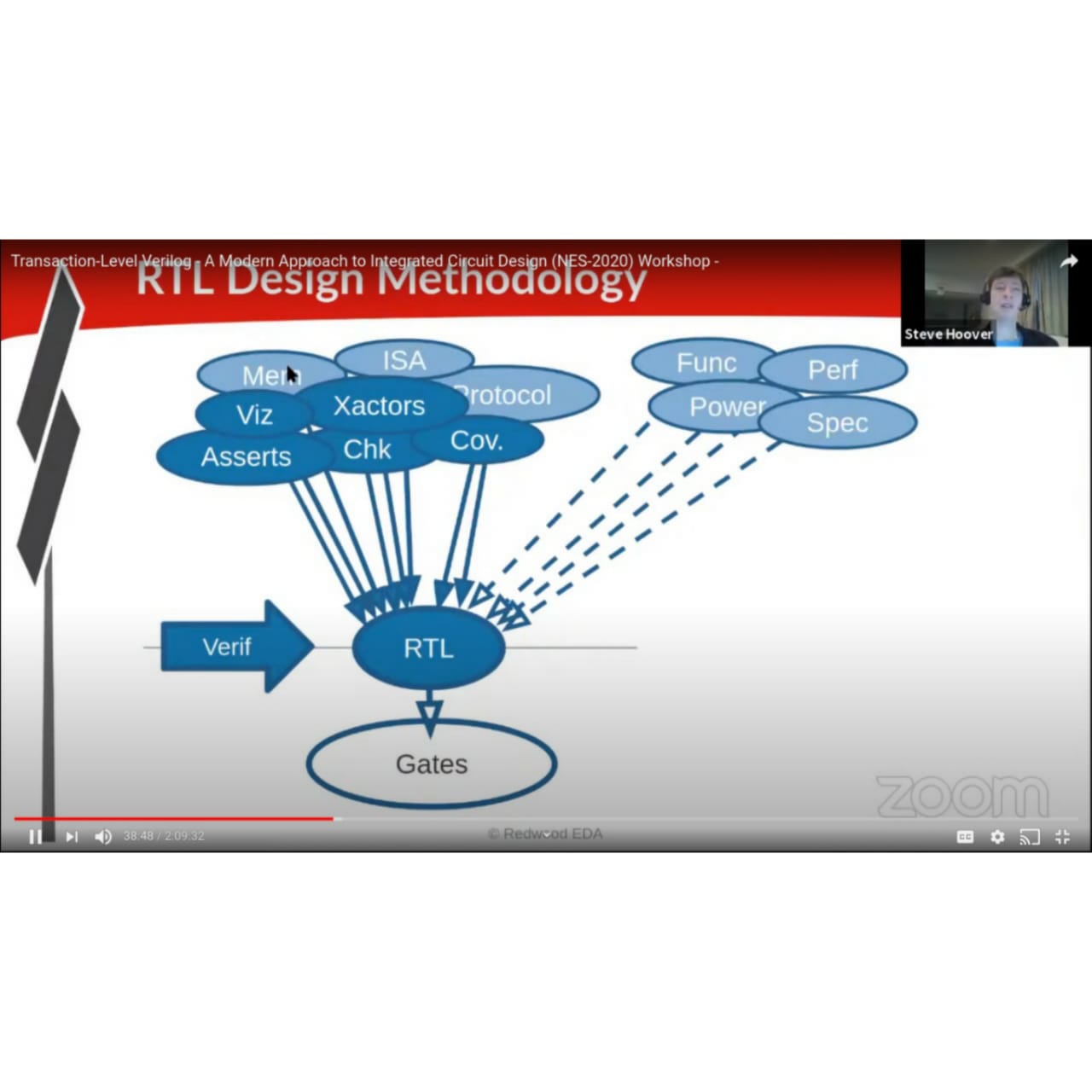

Enter Transaction-Level Verilog (TL-Verilog). Though it is an evolution of SystemVerilog, the sequential Verilog constructs (as well as many other constructs) become legacy features for backward compatibility. In place of a software abstraction, you get abstractions that match the mental models designers use to reason about their microarchitectures: pipelines, state, validity, hierarchy, and transactions. Leave loops, structs, and objects to software. And lest you think the introduction of abstract context adds bloat to the code, TL-Verilog models are generally half the size of their Verilog counterparts, with all the same detail. High-level context actually simplifies the logic expression. And, what does it buy you besides less typing? How about fewer bugs, better code organization, smoother hand-off, top-down design, easier microarchitectural changes, safe re-pipelining, and easier leverage and reuse. The mechanisms of TL-Verilog would be impractical in the face of sequential semantics.

The point is, using software, with sequential semantics, as a foundation for hardware modeling has led us down a limiting path, and TL-Verilog makes this point evident. TL-Verilog is specifically designed for modeling hardware -- more-so than any other language. Without the baggage of a software foundation, it is able to provide abstract context suited to hardware design with numerous benefits.

Want to know more about TL-VERILOG:

Check it out

Its really a game changer! Now you need to focus more on logic and thinking stuff rather than doing something that is already done.

THINK HARD, WORK SMART!!